## MULDEX IC FOR MULTIMEDIA TELESERVICES

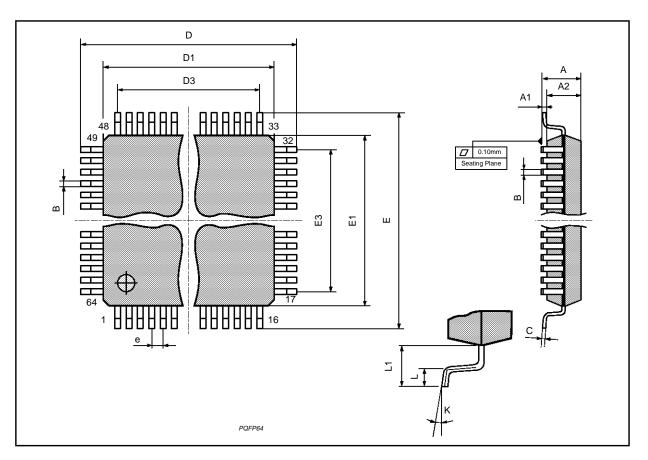

- HCMOS SEA OF GATE TECHNOLOGY

- 64 PINS QUAD FLAT PACKAGE

- TWO MODES OF OPERATION: STAND-ALONE, MICROPROCESSOR

- INTERFACE FOR 8/16/32 BIT MICROPROC-ESSORS

- TRANSMITTER FUNCTIONS: Implementation of two electrical interfaces:

64kbit/s only

- to 4 up to 32 Time Slot Multiplex.

Allocation of the multimedia frame structure in B channel for 32B channels.

3 input internal multiplexer can multiplex up to 3 sources within the 64kbit/s output stream. Serial/Parallel input to the AC data:

- Serial: using the 8th bit of the input stream.

- Parallel: using bytes provided by microprocessor.

Serial/parallel input for the seven sub-channels.

RECEIVER FUNCTIONS:

Implementation of two electrical interfaces: - 64kbit/s only

- to 4 up to 32 Time Slot Multiplex

Allocation of the multimedia frame structure in Bchannel of 32 channels.

3 Output internal demultiplexer can demultiplex up 3 signals provided by the 64kbit/s input stream.

Serial/parallel output for AC data:

- Serial: using the 8th bit of the output stream.

- Parallel: using bytes provided by microprocessor.

Serial/parallel output for the seven subchannels.

• OTHER GENERAL ASPECTS:

Interrupt procedures to access 16 input registers and 10 output registers.

Working with/without external byte synchronization depending on Protocol Select Pin and bit programmation.

The emitter and receiver provide superframe synchronization.

Error correction on BAS (up to two consecutive errors can be corrected, three are detected).

Fast receiver synchronization (parallel method).

#### DESCRIPTION

The H221/Muldex integrated circuit is a multiplex/demultiplex for a frame structure with 8-bit data channel. Manufactured using HCMOS "Sea of gates" technology, the device requires a single 5 V supply and is available in a 64 pin Quad Flat Package. The H221/Muldex implements the frame structure for a 64 kbit/s channel in audiovisual teleservices as defined by CCITT in the H.221 recommendation with automatic generation/decoding of FAW and error correction detection on BAS. It also implements the CRC4 algorithm for error detection on the sub-multiframe structure and allows the possibility of serial and/or parallel input/output of data channels (including the AC channel). In addition the multiframe structure is supported with automatic generation/decoding of the Multiframe Alignment Word and enabling of multiframe count. The H221/Muldex is controlled by a microprocessor using an 8-bit data bus or can function in a stand-alone mode; standard 64 kbit/s or time division multiplex interface are implemented.

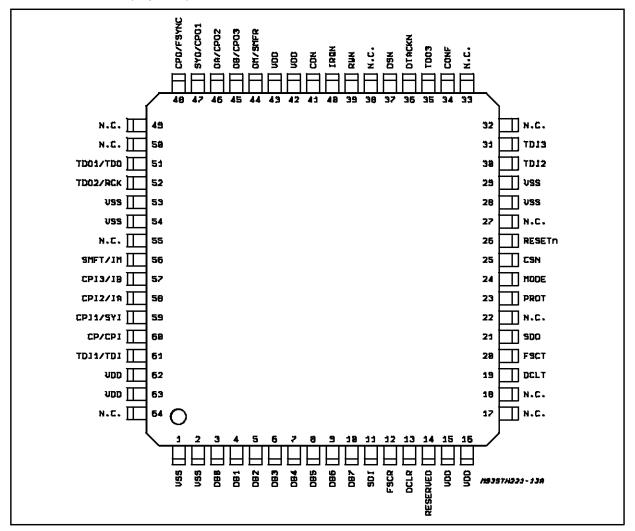

#### **PIN CONNECTION** (Top view)

| Symbol   | Pin | Symbol | Pin | Symbol    | Pin | Symbol   | Pin                   |

|----------|-----|--------|-----|-----------|-----|----------|-----------------------|

| CDN      | 41  | DB0    | 3   | SMFR/OM   | 44  | VSS      | 1,2,28,29,53,<br>54   |

| CONF     | 34  | DB1    | 4   | FSCR      | 12  | SMFT/IM  | 56                    |

| CP/CPI   | 60  | DB2    | 5   | FSCT      | 20  | TDI1/TDI | 61                    |

| CPI1/SYI | 59  | DB3    | 6   | FSYN/CPO  | 48  | TDI2     | 30                    |

| CPI2/IA  | 58  | DB4    | 7   | IRQN      | 40  | TDI3     | 31                    |

| CPI3/IB  | 57  | DB5    | 8   | MODE/TEST | 24  | TDO1/TDO | 51                    |

| CPO1/SYO | 47  | DB6    | 9   | PROT      | 23  | TDO2/RCK | 52                    |

| CP02/OA  | 46  | DB7    | 10  | RESETN    | 26  | TD03     | 35                    |

| CP03/OB  | 45  | DCLR   | 13  | RWN       | 39  | VDD      | 15,16,42,43,<br>62,63 |

| DSN      | 37  | DCLT   | 19  | SDI       | 11  | CSN      | 25                    |

| DTACKN   | 36  | SDO    | 21  |           |     |          |                       |

Pin 16 must not be connected.

| Table 2: Pin Descript |

|-----------------------|

|-----------------------|

| Pin  | Symbol        | Mode | Туре | Function                                                                                                                                                                                                                                                                                                                             |  |  |

|------|---------------|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 3-10 | DB0-DB7       | I/O  | CPU  | I/O Data $\mu$ P Interface.                                                                                                                                                                                                                                                                                                          |  |  |

| 11   | SDI           | 1    | Rx   | Serial Data Input. Input of serial stream from line into the receiver.<br>64 kbit/s or 256 kbit/s up to 2048kb/sec (GCI).                                                                                                                                                                                                            |  |  |

| 12   | FSCR          | I    | Rx   | Frame Syncro Rx. Octet synchronization (if present) for the receiver.                                                                                                                                                                                                                                                                |  |  |

| 13   | DCLR          | I    | Rx   | Data Clock Rx. Clock of input data for receiver.<br>64 khz or 512 up to 4096 khz (GCI)                                                                                                                                                                                                                                               |  |  |

| 19   | DCLT          | I    | Тх   | Data Clock Tx. Clock of output data from transmitter.<br>64 khz or 512 up to 4096 khz (GCI)                                                                                                                                                                                                                                          |  |  |

| 20   | FSCT          | I    | Тх   | Frame Syncro Tx. Octet syncronization (if present) for the transmitter.                                                                                                                                                                                                                                                              |  |  |

| 21   | SDO           | O*   | Тх   | Serial Data Output Output of serial stream from transmitter into B channel selected. Open drain in GCI mode.                                                                                                                                                                                                                         |  |  |

| 23   | PROT          | I    |      | Protocol select. Select of protocol implementation:<br>0 = 64 kbit/s<br>1 = Multiplex at 512 up to 2048kb/s.                                                                                                                                                                                                                         |  |  |

| 24   | MODE/<br>TEST | I    |      | CONF = 1 Test is given by this pin.<br>Specific test mode of the component. In normal operation, must be<br>0.                                                                                                                                                                                                                       |  |  |

|      |               |      |      | CONF = 0. Selection of working mode.<br>MODE = 0. Controlled by CPU (CPU mode)<br>MODE = 1. Stand Alone (S-A Mode). mode).<br>Test is given by Bit 3 of Command Register.                                                                                                                                                            |  |  |

| 25   | CSN           | I    | CPU  | <ul> <li>Chip Select. In CPU mode allows the selection of the component by the CPU:</li> <li>0 = The CPU can access internal registers using RWN, CDN, DSN signals.</li> <li>1 = The H221 is disabled.</li> <li>In S-A mode this pin represents the N5 bit of the H221 protocol (Enable/disable of the multiframe count).</li> </ul> |  |  |

| 26   | RESETN        | 1    |      | <b>Reset component</b> . Reset the H221 and initializes default conditions. Low Signal = active Minimum duration = $1\mu$ s.                                                                                                                                                                                                         |  |  |

| 30   | TDI 2         | I    | Tx   | <b>Terminal Data Input 2.</b> Serial input of data for the transmitter, clocked by CP. Data is shifted on the falling edge of CP. Usable only if CONF = 1 otherwise ignored.                                                                                                                                                         |  |  |

| 31   | TDI 3         | I    | Tx   | <b>Terminal Data Input 3.</b> Serial input of data for the transmitter.<br>Data is shifted on the falling edge of CP. Usable only if CONF = 1 otherwise ignored.                                                                                                                                                                     |  |  |

| 34   | CONF          | I    |      | <b>Configuration.</b><br>CONF = 0. CPI, TDI, SYI, IA, IB, IM, OM, TDO, CPO, SYO, OA, OB, RCK, Mode pins are validated.                                                                                                                                                                                                               |  |  |

|      |               |      |      | CONF = 1. CP, TDI 1/3, CPI 1/3, TDO 1/3, CPO 1/3, SMFT,<br>SMFR, TEST, FSYN pins are validated.                                                                                                                                                                                                                                      |  |  |

| 35   | TDO 3         | 0    | Tx   | <b>Terminal Data Output 3.</b> Serial Output of data received. Data is shifted on the rising edge of CP. If $CONF = 1$ : Open Drain else TDO3 = 0.                                                                                                                                                                                   |  |  |

| 36   | DTCAKN        | 0    | CPU  | <ul> <li>Data Acknowledge. Data acknowledge for writing from CPU and data ready for reading.</li> <li>1 = Data not yet ready or acknowledged.</li> <li>0 = Data ready or acknowledged.</li> <li>In S-A mode it represents the Aloc signal.</li> </ul>                                                                                |  |  |

| 37   | DSN           | I    | CPU  | <b>Data Strobe</b> . Strobe signal for data I/O from/to CPU.<br>0 = Data Valid on data bus.<br>In S-A mode it is used to strobe the BAS data on the data bus.                                                                                                                                                                        |  |  |

## Table 2: Pin Description.

| Pin | Symbol       | Mode | Туре | Function                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----|--------------|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 39  | RWN          | 1    | CPU  | <ul> <li>Read or Write. Indicates whether the next data transfer performed is a read or a write.</li> <li>0 = Write operation.</li> <li>1 = Read operation.</li> <li>In S-A mode it indicates the direction of the BAS data on data bus.</li> </ul>                                                                                                                                                                  |

| 40  | IRQN         | OD   | CPU  | Interrupt Request. When low indicates that the H221 is requesting interrupt service. This lead goes high when the CPU performs the interrupt acknowledge. It is an open drain so pull-up resistor is needed.<br>In S-A mode it represents the Eloc signal.                                                                                                                                                           |

| 41  | CDN          | I    | CPU  | Command or Data. Selection between the command register or<br>the data registers set.0 = The CPU accesses a data register.1 = The CPU accesses the command register.In S-A mode it enables the computing of the CRC4 value by the<br>transmitter.0 = Tx computers CRC4 value.1 = All 1's are transmitted on the CRC4 position (CRC4 disabled).                                                                       |

| 44  | SMFR/<br>OM  | 0    | Rx   | CONF = 1. Submultiframe received.<br>This signal goes high at the beginning of first bit of octet 1 of every<br>submultiframe. It returns low at the beginning of first bit of octet 83<br>of every submultiframe.<br>CONF = 0 Out Mask.<br>Frame synchronization; it goes high before the beginning of first bit                                                                                                    |

|     |              |      |      | of octet 1 of every frame. It returns low between the 16th and the 72nd octet, depending on the programmed conditions. Valid only when the receiver is frame aligned.                                                                                                                                                                                                                                                |

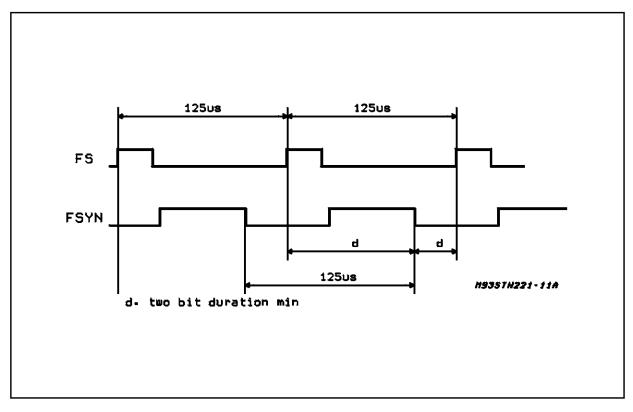

| 45  | CP03/<br>OB  | 0    | Rx   | CONF = 1. Clock pulse for data output 3. This signal is<br>configurated by CPS and WIN bits. It is associated to TDO3 data.<br>CONF = 0. Out multiplex addr. B.<br>LSB of the channel number of the bit on the TDO output.                                                                                                                                                                                           |

| 46  | CP02/<br>OA  | 0    | Rx   | CONF = 1. Clock pulse for data output 2. This signal is<br>configurated by CPS and WIN bits. It is associated to TDO2 data.<br>CONF = 0. Out multiplex addr. A. Together with OA and SYO<br>indicates the channel number of the bit on the TDO output. These<br>signals can be used to address an external demultiplexer<br>separating 8 sub-channels.                                                               |

| 47  | SYO/<br>CPO1 | 0    | Rx   | CONF = 1. Clock pulse for data output 1. This signal is<br>configurated by CPS and WIN bits. It is associated to TD01 data.<br>CONF = 0. Synchro Output MSB of the channel number of the bit<br>on the TDO output. It also represents the synchronization octet;<br>SYO is low at the beginning of the octet.                                                                                                        |

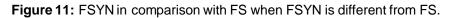

| 48  | FSYN/<br>CPO | I    | -    | CONF = 1. Frame Synchronization.<br>This 8kHz signal indicates the first bit of the first time slot for<br>TDO1, TDO2, TDO3, TDI1, TDI2, TDI3 multiplex.<br>CONF = 0 Clock Pulse Output;<br>Clock for the output of data from receiver. The clock input must<br>have a mimimum frequency of 64 KHz and a maximum frequency<br>of 2 MHz. Signals OA, OB and SYO have meaning only whne<br>CPO has a 64 KHz frequency. |

## Table 2: Pin Description.

| Pin | Symbol       | Mode | Туре         | Function                                                                                                                                                                                                                                                                       |

|-----|--------------|------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 51  | TDO1/<br>TDO | TS/O | Rx           | CONF = 1. Terminal Output 1.<br>Serial output of data received. Data is shifted on the rising edge of CP.<br>OPEN DRAIN                                                                                                                                                        |

|     |              |      |              | CONF = 0. Terminal Data Output.<br>Serial output of data received, clocked by CPO. Data is shifted on<br>the leading edge of CPO.                                                                                                                                              |

| 52  | TDO2/<br>RCK | TS/O | Rx           | CONF = 1. Terminal Output 2.<br>Serial output of data received.<br>Data is shifted on the rising edge of CP.<br>OPEN DRAIN                                                                                                                                                     |

|     |              |      |              | CONF = 0. Rx Clock.<br>A 64 KHz clock recovered by the receiver from the<br>incoming stream.                                                                                                                                                                                   |

| 56  | SMFT/<br>IM  | 0    | Тх           | CONF = 1. Submultiframe transmitted.<br>This signal goes high at the beginning of first bit of octet 1 of every<br>submultiframe. It returns low at the beginning of first bit of octet 8<br>of every submultiframe.                                                           |

|     |              |      |              | CONF = 0. Input Mask.<br>Input Mas. Frame synch; it goes high before the transmission of the<br>first bit of octet # 1 of every frame. It returns low between the 16th<br>and the 72nd octet, depending on the programmed conditions.                                          |

| 57  | CPI3/<br>IB  | 0    | Tx           | CONF = 1. Clock Pulse for data input 3. This signal is configurated by CPS and WIN bits. It is associated to TDI3 data.                                                                                                                                                        |

|     |              |      |              | CONF = 0. Input Mask.<br>In multiplex addr. B. LSB of the channel number of the bit on the<br>TDI input.                                                                                                                                                                       |

| 58  | CPI2/<br>IA  | 0    | Tx           | CONF = 1. Clock Pulse for data Input 2. This signal is configurated by CPS and WIN bits. It is associated to TDI2 data.                                                                                                                                                        |

|     |              |      |              | CONF = 0. In Multiplex Addr. A<br>In multiplex addr. A. Together with IA and SYI indicates the<br>channel number of the bit on the TDI input. These signals can be<br>used to address the multiplexing of 8 sub-channels.                                                      |

| 59  | CPI/<br>SYI  | 0    | Tx           | CONF = 1. Clock Pulse for data input 1. This signal is configurated by CPS and WIN bits. It is associated to TDI1 data.                                                                                                                                                        |

|     |              |      |              | CONF = 0. Input Synchronization .Input Sync. MSB of the channel<br>number of the bit on the TDI input. It also represents the sync of<br>the outgoing octet i.e. SYI is low at the beginning of the octet.                                                                     |

| 60  | CP/CPI       | 1    | Tx-Rx/<br>Tx | CONF = 1. Clock Pulse.<br>This signal is used to generate six clock pulses: CPI1, CPI2, CPI3<br>and CPO1, CPO2, CPO3. Its frequency is twice binary data rate of<br>TDI1, TDI2, TDB and TDO1, TDO2, TDO3 multiplex.<br>Minimum frequency 128kHz.<br>Maximum frequency 4096kHz. |

|     |              |      |              | CONF = 0. Clock Pulse input. Clock for the input of data into transmitter. The clock input must have a minimum frequency of 64kHz and a maximum frequency of 2 MHz. Signals IA, IB and SYI have meaning only when CPI has a 64kHz frequency.                                   |

| 61  | TDI1/<br>TDI |      | Tx           | CONF = 1. Terminal Data Input 1.<br>Serial input of data for the transmitter. Data is shifted on the falling<br>edge of CP.                                                                                                                                                    |

|     |              |      |              | CONF = 0. Terminal Data Input. Serial input of data for the transmitter, clocked by CPI. Data is shifted on the leading edge of CPI.                                                                                                                                           |

#### OVERVIEW

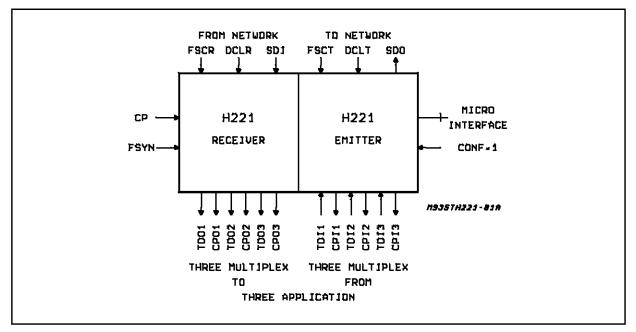

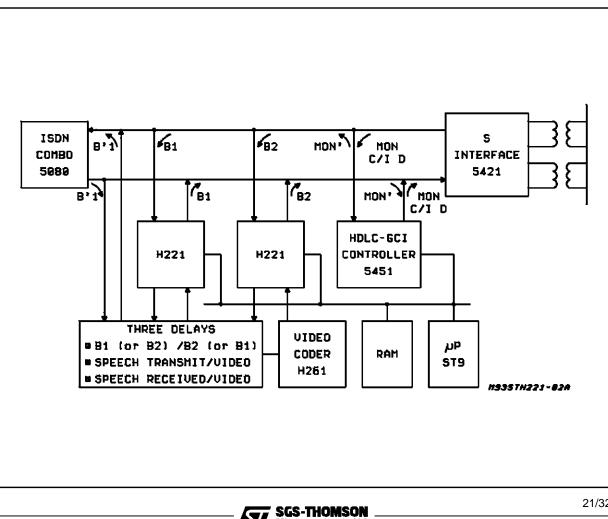

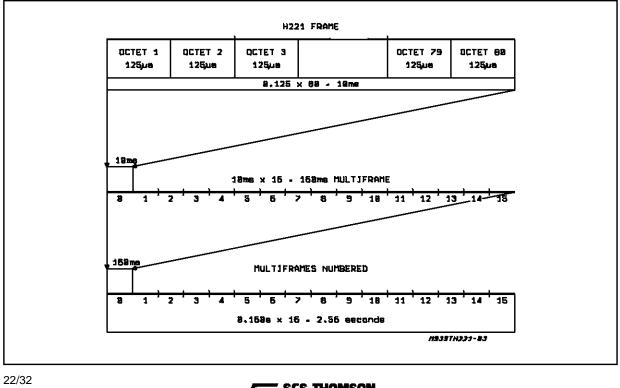

The H221/Muldex performs complete multiplexing/demultiplexing according to the CCITT H.221 recommendation. It generates and decodes frame and multiframe structure automatically without intervention by the host CPU. The host CPU must initialize the H221 registers and supply or read BAS and AC information upon request. The CPU is notified of important events via interrupt. The H221/Muldex contains a receiver, a transmitter and an interface unit (fig. 1).

#### ARCHITECTURE

#### Transmitter

The transmitter can work in two main modes: unframed or framed. In the first mode, octets to be transmitted are shifted out on the serial data output (SDO) without any data insertion or control; in framed mode, the transmitter constructs the frame, submultiframe and multiframe structure. Data is shifted on the rising edge of the data clock signal (DCLT).

In framed mode the transmitter handles bit # 8 of the octets: it puts into octets 1 to 16 information that identifies the frame structure (FAW, BAS, Parity, CRC4, A, E, according to the submultiframe); into octets 17 to 80 the transmitter puts the AC channel information.

This data can be sent to the AC register of the transmitter by the host CPU or can be the 8th bit of the incoming bit stream, depending on the configuration set by CPU. A request for AC data is made by the CPU via interrupt; the transmitter generates an interrupt request 1mS before it needs the data. After this time it transfers the AC data into internal register and starts the transmission of the next 8 octets. Then the cycle restarts with another interrupt request.

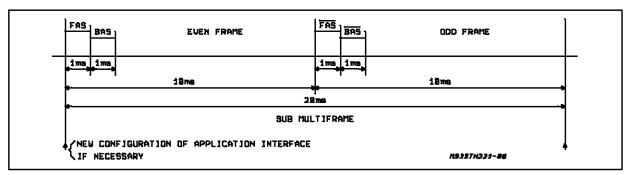

The same mechanism is applied to the BAS data request; SMFT pin generates a signal every 20ms.

This submultiframe transmit signal is at "1"during FAS transmitting. CPU can update if necessary BAS data and configuration registers TDI1R, TDI2R, TDI3R, when SMT is low. BAS data will be emitted during the next submultiframe and the new configuration of TDI1, TDI2, TDI3 multiplex will be actual after this next submultiframe. If not updated, old data is emitted.

The transmitter puts into the first bit of every information that identifies the multiframe structure; some are fixed and generated by the transmitter (MAW), others are variable (multiframe counter, L1, L2, L3, R bits and TEA). When enabled, the multiframe count is generated automatically by the transmitter, if disabled, all zeroes are transmitted; other bits are sent by the host CPU into the TFAS register. This data is transferred into internal register for transmission at the beginning of a multiframe (i.e. on the first bit of the frame # 0); if necessary data can be updated by the CPU before the end of a multiframe; no interrupt request is generated for this data.

The transmitter also computes the CRC4 value of a submultiframe and puts this value on the next odd frame according to the CCITT H221 recommendation; at reset, for the first two frames a zero value is transmitted; if the CRC4 computing is not enabled, the transmitter sends all ones in the CRC4 position.

#### Receiver

The receiver, like the transmitter, has two working modes: unframed and framed. In the first mode, octets received into the serial input (SDI) are shifted out on the terminal data (TDO) without any control or synchronism search; in framed mode, the receiver detects frame and multiframe alignment words (FAW and MAW) following procedures specified in CCITT H221 recommendation. When frame alignment is obtained, the receiver computes parity for BAS data; it uses this data for correcting up to two errors on BAS; 3 errors are detected.

If aligned, the receiver also decodes AC data; the availability of the data is signalled to the host CPU via interrupt; the CPU has 1ms to remove the data before the AC register is updated with the new value. The AC data is also available as the 8th bit of octets on terminal data output (TDO) when the component is receiving octets 17 to 80. The number of interrupt generated for the AC channel depends on the configuration set by CPU.

BAS register (RBAS) is updated every submultiframe when receiving octet 17 of the odd frame (i.e. after the parity has been verified); CPU can read BAS data when SMFR is low. SMFR pin generates a signal every 20ms. This Submultiframe Receive Signal is at "1"during an even frame and FAS and BAS receiving of odd frame. After reading BAS data, CPU can load immediately into TDO1R, TDO2R, TDO3R register when SMFR is yet low to change the configuration of TDO1, TDO2, TDO3 multiplex if necessary. Errors detected on BAS data (corrected or not) are signalled to the host CPU via interrupt; reading the receiver status register the CPU can determine the type of error.

The data on the BAS register is not valid if errors on BAS are not recoverable. In the first bit of every frame the receiver reads information concerning multiframe structure; registers that hold this information (multiframe counter (RC), L1, L2, L3, R bits and TEA (RFAS)) are updated at the beginning of a multiframe; the CPU can read multiframe data at any time except on the first octet of the first frame of a multiframe.

The receiver also computes the CRC4 value of a submultiframe and compares it with the received value of CRC4; if discrepancies are found, bit Eloc is set and an interrupt is generated; error interrupts are generated at the beginning of a frame only when some error condition are present.

#### Interface

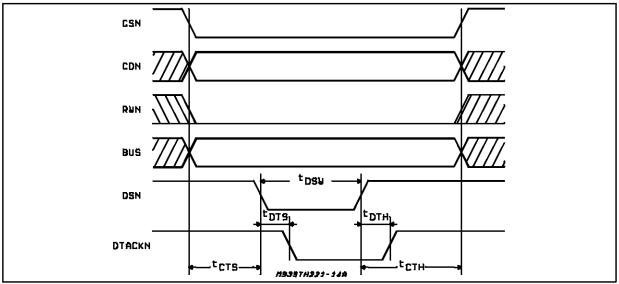

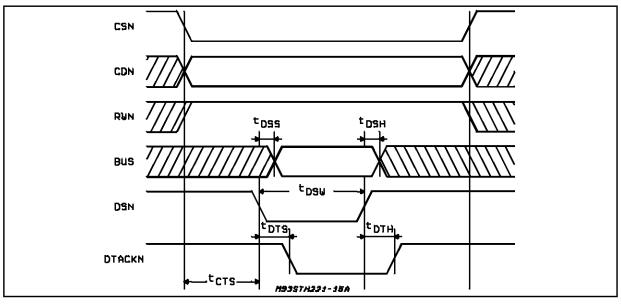

The interface unit provides interface between the host CPU and the H221 Muldex transmitter and receiver via data bus and some control signals. The interface holds general purpose register and decoding logic for the addressing of transmitter and receiver registers. Using data-strobe/dataacknowledge protocol, the H221/Muldex can interface CPU that use synchronous or asynchronous read/write cycles.

#### **PRINCIPLES OF OPERATION**

#### **CPU Interface**

The CPU has direct access into two register, command or data, using the CDN signal. The data register is split in 16 registers; the address of the data register is specified in the command register. The CPU configures the H221/Muldex by writing the command and data registers. Status information can be accessed by reading one of the status registers and is used to monitor the H221/Muldex operation. The most useful information is coded in the command/status register for fast access by the CPU.

#### H221 Registers

The H221/Muldex registers are divided into four classes: command/status, receiver, transmitter, test.

**Command/Status Register**. Direct access by CPU when CDN signal is high; contains interrupt and error flags, controls the addressing of data registers, the clearing of interrupt flags, the test mode and the start of the transmitter.

**Receiver Registers.** These registers contain information received: multiframe data, BAS data, AC data, octet. Other registers contain status information of the receiver: frame and multiframe counters, AC counter, status bit indicating level of synchronization achieved (octet, frame, multiframe).

**Transmitter Registers.** These registers contain information to be transmitted: multiframe data, BAS data, AC data, octect. Other registers contain status information of the transmitter: frame and multiframe counters, AC counter, bits programming the operating mode of the transmitter.

**Test Register**. These registers contain data used for the testing of the component; not used in normal operation.

Table 3: Common/Status Register Definition.

| Bit           | 7  | 6  | 5  | 4 | 3    | 2  | 1  | 0  |

|---------------|----|----|----|---|------|----|----|----|

| (Write) Field | IR | IT | IE | S | W3/T | W2 | W1 | W0 |

| Bit | Symbol | Name/Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                       |                                    |                                     |                                       |                |  |  |

|-----|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|------------------------------------|-------------------------------------|---------------------------------------|----------------|--|--|

| 0   | WO     | Data Register<br>CONF = 1] as                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Address (bit 0).<br>the address of th | Interpreted with e data register a | W1 (bit 1) and<br>is indicated by t | W2 (bit 2) and W3 he following table: | [(bit 3) + if  |  |  |

|     |        | W3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | W2                                    | W1                                 | WO                                  | Write                                 | Read           |  |  |

|     |        | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0                                     | 0                                  | 0                                   | TFAS                                  | RFAS           |  |  |

|     |        | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0                                     | 0                                  | 1                                   | TBAS                                  | RBAS           |  |  |

|     |        | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0                                     | 1                                  | 0                                   | TAC                                   | RAC            |  |  |

|     |        | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0                                     | 1                                  | 1                                   | TEST                                  | TC             |  |  |

|     |        | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1                                     | 0                                  | 0                                   | TEST                                  | RC             |  |  |

|     |        | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1                                     | 0                                  | 1                                   | COND                                  | RXST           |  |  |

|     |        | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1                                     | 1                                  | 0                                   | ACS/TEST                              | RTACC          |  |  |

|     |        | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1                                     | 1                                  | 1                                   | TPD                                   | RPD            |  |  |

|     |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                       | Available onl                      | y if CONF = 1                       |                                       |                |  |  |

|     |        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0                                     | 0                                  | 0                                   | TSAA                                  | TBCR           |  |  |

|     |        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0                                     | 0                                  | 1                                   | TDO1R                                 | -              |  |  |

|     |        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0                                     | 1                                  | 0                                   | TDO2R                                 | -              |  |  |

|     |        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0                                     | 1                                  | 1                                   | TDO3R                                 | -              |  |  |

|     |        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1                                     | 0                                  | 0                                   | TSAN                                  | RBCR           |  |  |

|     |        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1                                     | 0                                  | 1                                   | TDI1R                                 | -              |  |  |

|     |        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1                                     | 1                                  | 0                                   | TDI2R                                 | -              |  |  |

|     |        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1                                     | 1                                  | 1                                   | TDI3R                                 | -              |  |  |

|     |        | Forced to 1 if I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | MODE pin is high                      | and CONF = 0.                      |                                     |                                       |                |  |  |

| 1   | W1     | Data Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Address (bit 1).                      | Forced to 0 whe                    | en MODE pin is                      | high and CONF =                       | 0.             |  |  |

| 2   | W2     | Data Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Address (bit 2).                      | Forced to 0 whe                    | en MODE pin is                      | high and CONF =                       | 0.             |  |  |

| 3   | W3/T   | Data Register Address (bit 3) if CONF = 1.<br>CR Test if CONF = 0.<br>Specifies test mode of the component. In normal operation must be 0. T is cleared by hardware<br>reset or by software reset (bit RSN of COND register).<br>If CONF = 1, this function is performed through pin MODE/TEST                                                                                                                                                                                                     |                                       |                                    |                                     |                                       |                |  |  |

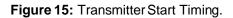

| 4   | S      | <b>Start/Interrupt Enable</b> . When this bit goes high, the transmitter starts transmitting the first bit of the first frame of a multiframe. If it remains high, generation of all interrupts is enabled. If it returns low interrupts are disabled. Two consecutive writes to this bit (1-0) are sufficient to start the transmitter. The transmitter starts on the second falling edge of SYI signal (fig. 5). S is cleared by hardware reset or by software reset (bit RSN of COND register). |                                       |                                    |                                     |                                       |                |  |  |

| 5   | IE     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                       |                                    |                                     | corresponding inter                   |                |  |  |

| 6   | IT     | Transmitter Ir<br>flag.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | terrupt Acknow                        | ledge. Writing 1                   | on this bit clea                    | rs the correspondir                   | ng interrupt   |  |  |

| 7   | IR     | Receiver Inter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | rrupt Acknowled                       | <b>Ige</b> . Writing 1 or          | n this bit clears t                 | he corresponding i                    | nterrupt flag. |  |  |

## Table 3: Common/Status Register Definition. (Continued)

| Bit          | 7  | 6  | 5  | 4    | 3    | 2   | 1  | 0 |

|--------------|----|----|----|------|------|-----|----|---|

| (Read) Field | IR | IT | IE | ELOC | ALOC | EBC | EB | 0 |

| Bit | Symbol | Name/Description                                                                                                                                                                              |

|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | _      | Unused bit. Read always as zero.                                                                                                                                                              |

| 1   | EB     | <b>BAS Data Error</b> When 1 indicates an unrecoverable error on the BAS data. This bit is updated on a submultiframe basis.                                                                  |

| 2   | EBC    | <b>BAS Data Error Recovered</b> When 1 indicates that BAS data has been received with an or 2 errors and that error has been corrected by the error correction logic.                         |

| 3   | ALOC   | <b>Local Alignment</b> . When 0 indicates that the receiver is aligned on frame and multiframe. The same bit is transmitted as bit A of the frame if ASEL bit of ACS/TEST register allows it. |

| 4   | ELOC   | <b>Local Error</b> . When 1 indicates a difference between the CRC4 value calculated by the receiver and the CRC4 received. The same bit can be transmitted as bit E of the frame             |

| 5   | IE     | <b>Error Interrupt Flag.</b> When 1 indicates that an error interrupt has been generated by the component. It returns 0 on error interrupt acknowledge.                                       |

| 6   | IT     | <b>Transmitter Interrupt Flag</b> . When 1 indicates that a transmitter interrupt has been generated by the component. It returns 0 on transmitter interrupts acknowledge.                    |

| 7   | IR     | <b>Receiver Interrupt Flag.</b> When 1 indicates that a receiver interrupt has been generated by the component. It returns 0 on receiver interrupt acknowledge.                               |

| Bit                          | 7   | 6      | 5  | 4   | 3 | 2  | 1  | 0  |

|------------------------------|-----|--------|----|-----|---|----|----|----|

| (Write) Field                | EPI | SYNEXT | N5 | TEA | R | L3 | L2 | L1 |

| Hardware RESET configuration | 0   | 1      | Х  | 0   | 0 | 0  | 0  | 0  |

Table 4: TFAS Register Definition (Address 0000).

| Bit | Symbol   | Name/Description                                                                                                                                                                                                                                                                     |

|-----|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0-3 | L1-L3, R | L1-L3, R bits. L1-L3 and R bits of H221 multiframe structure. Cleared by hardware or software reset.                                                                                                                                                                                 |

| 4   | TEA      | TEA bit. Terminal Equipment Alarm bit to be transmitted. Cleared by hardware or software reset.                                                                                                                                                                                      |

| 5   | N5       | <b>N5 bit</b> . Multiframe count enable. When 1 the transmitter counts multiframe sending multiframe number in descending order on bit N1N4 (N1 = LSB). No default on reset.                                                                                                         |

| 6   | SYNEXT   | <b>Transmitter Octet Syncro Valid.</b> Specifies if external octet synchro is valid. If 1, the external octect syncro is present and valid; if 0, the octet synchro may be present but it is not taken into account by transmitter. Hardware or software reset forces this bit to 1. |

| 7   | EPI      | <b>Enable Parallel Input</b> . When 1 enables parallel input of data to be transmitted using TPD register. If this bit is 0 data enters serially through the TDI input. Cleared by hardware or software reset.                                                                       |

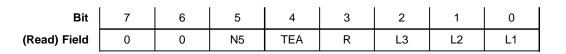

Table 5: RFAS Register Definition (Address 0000).

| Bit | Symbol   | Name/Description                                                                                                    |

|-----|----------|---------------------------------------------------------------------------------------------------------------------|

| 0-3 | L1-L3, R | L1-L3, R bits. L1-L3 and R bits of H221 multiframe structure.                                                       |

| 4   | TEA      | TEA bit. Terminal Equipment Alarm bit received.                                                                     |

| 5   | N5       | <b>N5 bit</b> . Enable multiframe count bit received. If 1 the remote transmitter has multiframe numbering enabled. |

| 6-7 | _        | Unused bits. Read as zero.                                                                                          |

Table 6: TBAS and RBAS Register Definition (Address 0001).

| Bit   | 7              | 6  | 5  | 4  | 3  | 2  | 1              | 0  |

|-------|----------------|----|----|----|----|----|----------------|----|

| Field | b <sub>0</sub> | b1 | b2 | b3 | b4 | b5 | b <sub>6</sub> | b7 |

| Bit | Symbol | Name/Description                                                                                                                                             |

|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0-7 | b0b7   | <b>BAS Data</b> . BAS data to be transmitted (TBAS Register write) or received (RBAS Register read). $b_0$ is the MSB and $b_7$ the LSB as defined by CCITT. |

Rem: Hardware RESET is inactive on configuration.

Table 7: TAC and RAC Register Definition (Address 0010).

| Bit   | 7               | 6               | 5               | 4               | 3               | 2               | 1               | 0               |

|-------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| Field | AC <sub>7</sub> | AC <sub>6</sub> | AC <sub>5</sub> | AC <sub>4</sub> | AC <sub>3</sub> | AC <sub>2</sub> | AC <sub>1</sub> | AC <sub>0</sub> |

| Bit | Symbol                          | Name/Description                                                                                                                                                                                                    |

|-----|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0-7 | AC <sub>0</sub> AC <sub>7</sub> | <b>AC Data</b> . AC data to be transmitted (TAC Register write) or received (RAC Register read). In TAC register $AC_0$ is the first bit transmitted while in RAC register $AC_0$ represents the last bit received. |

Rem: Hardware RESET is inactive on configuration.

Table 8: TC Register Definition (Address 0011).

| Bit          | 7      | 6      | 5      | 4               | 3      | 2               | 1      | 0               |

|--------------|--------|--------|--------|-----------------|--------|-----------------|--------|-----------------|

| (Read) Field | $TN_4$ | $TN_3$ | $TN_2$ | TN <sub>1</sub> | $TF_3$ | TF <sub>2</sub> | $TF_1$ | TF <sub>0</sub> |

| Bit | Symbol     | Name/Description                                                                                                                                            |

|-----|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0-3 | $TF_0TF_3$ | <b>Transmitter Frame Counter</b> . Indicates the frame number in transmission (i.e. the frame position within the multiframe structure). $TF_0$ is the LSB. |

| 4-7 | $TN_1TN_4$ | <b>Transmitter Multiframe Counter</b> . Indicates multiframe number in transmission and represents bit N1N4 of the multiframe structure. $TN_1$ is the LSB. |

Rem: Write register used for TEST only : No access to user

| Bit          | 7               | 6               | 5               | 4               | 3               | 2               | 1               | 0      |

|--------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|--------|

| (Read) Field | RN <sub>4</sub> | RN <sub>3</sub> | RN <sub>2</sub> | RN <sub>1</sub> | RF <sub>3</sub> | RF <sub>2</sub> | RF <sub>1</sub> | $RF_0$ |

|     |   |   |   | _ | _ |   |

|-----|---|---|---|---|---|---|

| Bit | 7 | 6 | 5 | 4 | 3 | 2 |

| Bit | Symbol | Name/Description                                                                                                                                   |  |  |  |  |  |

|-----|--------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 0-3 | RF₀RF3 | <b>Receiver Frame Counter</b> . Indicates the receiving frame number (i.e. the frame position within the multiframe structure). $RF_0$ is the LSB. |  |  |  |  |  |

| 4-7 | RN₁RN₄ | <b>Receiver Multiframe Counter</b> . Indicates bit N1 N4 of the received multiframe structure. RN <sub>1</sub> is the LSB.                         |  |  |  |  |  |

Rem: WRITE register used for TEST only : No access to user.

Table 9: RC Register Definition (Address 0100).

## Table 10: COND Register Definition (Address 0101).

| Bit                             | 7    | 6     | 5      | 4   | 3   | 2     | 1     | 0   |

|---------------------------------|------|-------|--------|-----|-----|-------|-------|-----|

| (Write) Field                   | ENEL | ENCRC | SYNEXR | RSN | ACS | N5IEN | B1B2N | FUN |

| Hardware RESET<br>Configuration | 1    | 0     | 0      | 1   | 1   | 1     | 1     | 1   |

| Bit | Symbol | Name/Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | FUN    | <b>Framed or Unframed Mode</b> . Specifies if the transmitter generates frame and multiframe structure. If 1 the transmitter sends FAS, BAS, AC, CRC4, A, E and multiframe information on bit 8 of transmitting data. If 0 the 8th bit is passed as is from TDI input to SDO output. Hardware reset forces this bit to 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1   | B1B2N  | <b>B1 or B2 Position</b> . When GCI mode active and CONF set to 0, specifies the position of the octet on the input or output data stream. If 1 the octet is placed on B1 position; if 0 on B2 position. In 64 kbit/s mode or CONF set to 1, B1B2N has no meaning. Hardware reset forces this bit to 1. When CONF is set to 1, the desired position is defined through bits 4 to 0 of TSAN register (TSN4, TSN3, TSN2, TSN1, TSN0).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2   | N5IEN  | <b>N5 Internal or External</b> . Specifies the source of N5 bit (multiframe count enable). If 1 the N5 bit of the transmitter is the complement of the Aloc bit of the receiver. In this case the transmitter starts multiframe count automatically when the receiver is aligned. If N5IEN = 0, the N5 bit of the transmitter is the bit contained in the TFAS register. In this case the transmitter starts multiframe count when the CPU writes 1 on N5 bit of TFAS register. Hardware reset forces this bit to 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3   | ACS    | <b>AC Mode Select</b> . Specifies the way AC data is exchanged with the terminal: parallel or mixed mode (serial/parallel). If 0, AC data are sent to H221/Muldex by CPU through data bus 8 bits at a time (parallel mode) upon interrupt request. Eight interrupt requests are generated by the transmitter at the beginning of octets 9, 17, 25, 33, 41, 49, 57, 65; the CPU has 1mS to update the AC register (TAC), then the 8 bits of AC are transmitted (for data requested on octet 9 the transmission starts at octet 16 and ends at octect 24, AC0 bit first). Eight interrupt requests are generated by the receiver at the beginning of octets 25, 33, 41, 49, 57, 65, 73, 1; the CPU has 1ms to remove data from AC register (RAC), then the AC register is updated with the new received data (in octet 25 is presented data received in octets 16 to 24, AC0 bit first). If the ACS bit is 1, AC data are sent to H221/Muldex in a mixed mode (parallel/serie). Parallel data are requested first; the number of parallel AC data is specified on bits $ACSE_0$ $ACSE_2$ of $ACS/TEST$ register. The remaining part of the AC data is generated only for parallel data. The receiver gives AC data simultaneously in both ways but generates interrupt request only for parallel data. Hardware reset forces this bit to 1. |

Table 10: COND Register Definition (Continued).

| Bit | Symbol | Name/Description                                                                                                                                                                                                                                                                                                                                                         |

|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4   | RSN    | <b>Reset Software</b> . When 0, this bit forces reset state of the component and initializes default conditions in all registers except the COND register itself. Hardware reset forces this bit to 1.                                                                                                                                                                   |

| 5   | SYNEXR | <b>Receiver Octet Syncro Valid</b> . Specifies if external octet synchro is valid. If 1, the external octet synchro is present and valid; if 0, the octet synchro may be present but it is not taken into consideration by the receiver. Hardware reset forces this bit to 0.                                                                                            |

| 6   | ENCRC  | <b>Enable CRC4 Calculation</b> . Specifies whether the transmitter has to calculate and transmit the value of CRC4. If 1, the transmitter calculates and transmits the CRC4 value; if 0, the value of CRC4 is not calculated and all ones are transmitted on the CRC4 position. Hardware reset forces this bit to 0.                                                     |

| 7   | ENEL   | <b>Enable transmission of Eloc.</b> Specifies is the Eloc signal is passed from the receiver to the transmitter. If 1, the receiver passes the Eloc bit (the result of comparison between CRC4 received and calculated) to the transmitter. If 0, no value is transferred and the transmitter always sends 0 on the E bit position. Hardware reset forces this bit to 1. |

Table 11: RXST Register Definition (Address 0101).

| Bit          | 7     | 6 | 5 | 4  | 3  | 2  | 1 | 0 |

|--------------|-------|---|---|----|----|----|---|---|

| (Read) Field | CRCA1 | _ | _ | SM | SF | SO | E | А |

| Bit | Symbol | Name/Description                                                                                                                                                                                                                                                   |

|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | А      | Alignment Loss. When 1 indicates a loss of alignment in the remote receiver. It represents the A bit received in odd frames.                                                                                                                                       |

| 1   | E      | <b>CRC4 Error</b> . When 1 indicates an error on the CRC4 computing by the remote receiver. It re presents the E bit received in odd frames.                                                                                                                       |

| 2   | SO     | <b>Octet Synchronization</b> . When 1 indicates that the receiver has achieved octet synchronization by recognizing the FAS position on the frame structure.                                                                                                       |

| 3   | SF     | <b>Frame Synchronization</b> . This bit goes high when the receiver validates the received frame as specified by CCITT H221 rec. It remains high until a loss of frame alignment is recognized.                                                                    |

| 4   | SM     | <b>Multiframe Synchronization</b> . This bit goes high when multiframe alignment is achieved by the receiver that recognizes the multiframe alignment signal. It returns low when three consecutive multiframe alignment signals have been received with an error. |

| 5-6 | _      | Unused bits. Read undefined.                                                                                                                                                                                                                                       |

| 7   | CRCA1  | <b>CRC4 All Ones</b> . When 1 indicates that the received CRC4 data contains all ones. This can be a symptom that indicates the disabling of the CRC4 calculation by the remote transmitter.                                                                       |

| Bit                             | 7                 | 6     | 5                 | 4    | 3    | 2    | 1    | 0   |

|---------------------------------|-------------------|-------|-------------------|------|------|------|------|-----|

| (Write) Field                   | ACSE <sub>2</sub> | ACSE1 | ACSE <sub>0</sub> | RRES | ASEL | AEXT | RSBT | RCL |

| Hardware RESET<br>Configuration | 0                 | 0     | 0                 | 0    | 0    | Х    | 0    | Х   |

Table 12: ACS/TEST Register Definition (Address 0110).

| Bit | Symbol            | Name/Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                              |                     |                       |                                                |                                            |                                     |  |  |  |

|-----|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------------------|------------------------------------------------|--------------------------------------------|-------------------------------------|--|--|--|

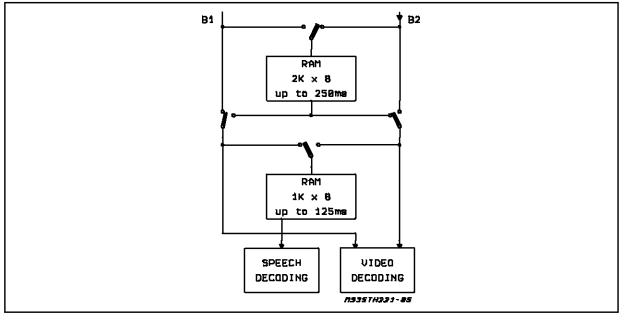

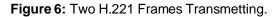

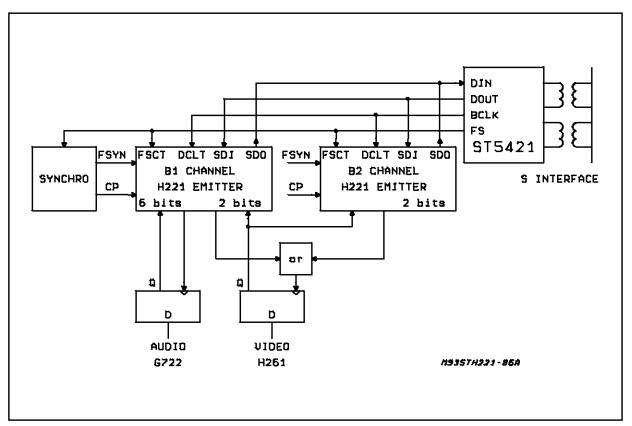

| 0   | RCL               | <b>Recirculate Control</b> . Specifies recirculating of the output stream into the receiver for local testing purposes. If 1, the output of the transmitter is internally recirculated into the receiver. The output pin (SDO) is forced to 1 when in 64 kbit/s mode (3-state when in GCI mode), the data on the input pin (SDI) is ignored. This bit has meaning only when bit T of command register is 1.                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                              |                     |                       |                                                |                                            |                                     |  |  |  |